# **JSKT120/JSKH120**

### **Description:**

- 1) A package of series of two chips.

- 2) With high thermal conductivity DBC as the insulation.

- 3) Welding by vacuum welding technology, which provide high reliability.

## **Typical Application:**

DC motor control, temperature control and light control system.

## **Absolute Maximum Ratings** (Packaged into modules, unless otherwise specified, T<sub>CASE</sub>=25℃)

| Parameter                                 | Test Conditions                                          | Symbol                                 | Values    |      |                  |            |

|-------------------------------------------|----------------------------------------------------------|----------------------------------------|-----------|------|------------------|------------|

|                                           |                                                          |                                        | 12        | 16   | 18               | Unit       |

| Operating junction temperature range      |                                                          | Tj                                     | -40-125   |      |                  | $^{\circ}$ |

| Storage temperature range                 |                                                          | T <sub>stg</sub>                       | -40-125   |      | $^{\circ}$       |            |

| Repetitive peak off-state voltage         | Tj=25℃                                                   | V <sub>DRM</sub>                       | 1200      | 1600 | 1800             | V          |

| Repetitive peak reverse voltage           | Tj=25℃                                                   | V <sub>RRM</sub>                       | 1200      | 1600 | 1800             | V          |

| Non-repetitive peak off-state voltage     | T <sub>j</sub> =25℃                                      | V <sub>DSM</sub>                       | 1300      | 1700 | 1900             | V          |

| Non-repetitive peak reverse voltage       | T <sub>j</sub> =25℃                                      | V <sub>RSM</sub>                       | 1300      | 1700 | 1900             | V          |

| Average on-state current                  | T <sub>C</sub> =85℃                                      | I <sub>T(AV)</sub> /I <sub>F(AV)</sub> | 120       |      | Α                |            |

| Peak on-state surge current               | t <sub>P</sub> =10ms V <sub>R</sub> =0.6V <sub>RRM</sub> | ITSM/IFSM                              | 2500      |      | Α                |            |

| I <sup>2</sup> t value for fusing         | t <sub>P</sub> =10ms V <sub>R</sub> =0.6V <sub>RRM</sub> | l <sup>2</sup> t                       | 31250     |      | A <sup>2</sup> s |            |

| Critical rate of rise of on-state current | Ig=2×IgT                                                 | dl/dt                                  | 150       |      | A/µs             |            |

| Isolation voltage                         | A.C 50Hz(1s/1min)                                        | Viso                                   | 3600/3000 |      | V                |            |

#### **Electrical Characteristics** (Packaged into modules, unless otherwise specified, T<sub>CASE</sub>=25°C)

| Parameter                         | Test Conditions      | Symbol            | Values | Unit |

|-----------------------------------|----------------------|-------------------|--------|------|

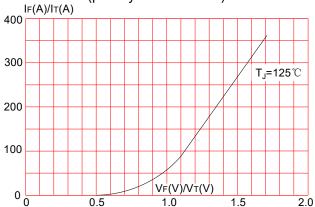

| Peak on-state voltage             | I⊤=360A t⊳=380µs     | V <sub>TM</sub>   | ≤1.8   | V    |

| Threshold voltage                 | T <sub>j</sub> =125℃ | V <sub>TO</sub>   | ≤0.95  | V    |

| Dynamic resistance                | T <sub>j</sub> =125℃ | R₀                | ≤2.1   | mΩ   |

| Repetitive peak off-state current | VD=VDRM<br>Tc=25°C   | I <sub>DRM1</sub> | ≤100   | μA   |

|                                   | Tc=125℃              | I <sub>DRM2</sub> | ≤40    | mA   |

| Repetitive peak reverse current  | VR=VRRM<br>Tc=25℃<br>Tc=125℃                                          | Irrm1<br>Irrm2 | ≤100<br>≤40  | μA<br>mA |

|----------------------------------|-----------------------------------------------------------------------|----------------|--------------|----------|

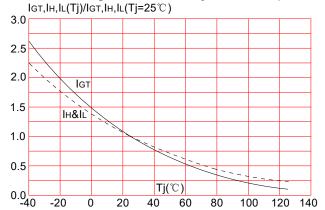

| Triggering gate current          | V <sub>D</sub> =12V R <sub>L</sub> =30Ω                               | Ідт            | 20-120       | mA       |

| Holding current                  | I <sub>T</sub> =1A                                                    | Ін             | ≤250         | mA       |

| Latching current                 | Ig=1.2 Igт                                                            | l <sub>L</sub> | ≤300         | mA       |

| Triggering gate voltage          | V <sub>D</sub> =12V R <sub>L</sub> =30Ω                               | $V_{GT}$       | ≤1.8         | V        |

| Non triggering gate voltage      | V <sub>D</sub> =V <sub>DRM</sub> T <sub>j</sub> =125 °C               | $V_{GD}$       | ≥0.25        | V        |

| Critical rate of rise of voltage | V <sub>D</sub> =2/3V <sub>DRM</sub> T <sub>j</sub> =125℃<br>Gate Open | dv/dt          | ≥1000        | V/µs     |

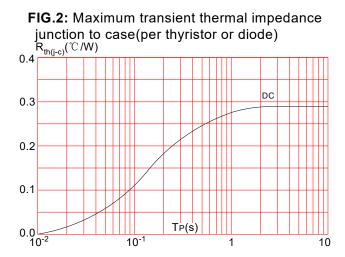

| Thermal resistance               | Junction to case<br>Case to heatsink                                  | Rth(j-c)       | 0.29<br>0.21 | °C/W     |

# **Mechanical Characteristics**

| Module size                                                                                                  | 93.5mm×21mm                             |  |  |

|--------------------------------------------------------------------------------------------------------------|-----------------------------------------|--|--|

| Module height                                                                                                | 31mm                                    |  |  |

| Terminal distance of (1) /(2) /(3)                                                                           | 20mm                                    |  |  |

| Mounting torque(M5)                                                                                          | 5±15%Nm                                 |  |  |

| Terminal torque(M5)                                                                                          | 3±15%Nm                                 |  |  |

| 4-2.8×0.80<br>93.5±0.75<br>3-M5<br>93.5±0.75<br>3-10<br>15.4±0.50 20.0±0.50 20.0±0.50 14.8±0.50<br>80.0±0.50 | (1) (2) (3) (3) (5) (6) (4) JSKH symbol |  |  |

#### **Instructions and Precautions**

- 1) There is no severe vibration and shock in operating environment, and there should be no impurity and atmosphere which may corrode metal and damage the insulation in the air-dielectric.

- 2) The operating condition of the product can't out of range of the above parameters.

- 3) When the product is installed on the radiator, the radiator's surface should be confirmed flat, smooth, wipe clean with alcohol, and coated evenly with a layer of thermal grease which thickness is moderate on the contact surface between product and radiator. When the module is fastened on the surface of the radiator, the M5 or M6 screws and spring washers are used and fastened with 5NM torque. After the module is operated 1 hour, all screws must be refastened.

- 4) The connection with the main electrode of module can use copper, welding, socket and so on. The contact surface should be smooth and flat, which make good contact. While the connection with the control electrode of module is installed, attention should be paid to the corresponding connection of each pin. After the completion of the connection, do not plug and pull out the lead of the control electrode freely.

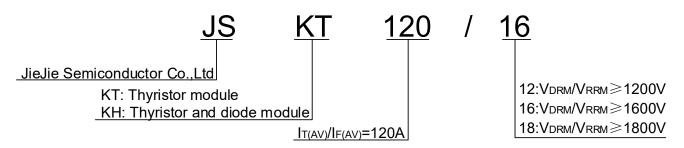

#### **Ordering Information**

#### **Performance Curves**

FIG.1:Power dissipation vs. on-state current (per thyristor or diode) Pτ(av)/Pr(av)(W) 250 rec.180 200 120 cont. 90 150 30 rec.15 100 50 IT(AV)/IF(AV)(A)0 0 120 140 160 180 100

**FIG.3:**Forward characteristics (per thyristor or diode)

**FIG.4:** Relative variations of gate trigger current, holding current and latching current versus junction temperature

Information furnished in this document is believed to be accurate and reliable. However, JieJie Semiconductor Co.,Ltd assumes no responsibility for the consequences of use without consideration for such information nor use beyond it.

Information mentioned in this document is subject to change without notice, apart from that when an agreement is signed, JieJie complies with the agreement.

Products and information provided in this document have no infringement of patents. JieJie assumes no responsibility for any infringement of other rights of third parties which may result from the use of such products and information.